来源:内容由半导体行业观察(ID:icbank)编译自「日经」,谢谢。

据日经报道,在美国竞争对手英特尔表示计划夺取芯片行业领导地位的第二天,台积电宣布,公司已获得建造其最先进芯片工厂的最终批准。

台积电计划在台湾最重要的芯片制造中心之一的新竹建立一个 2 纳米芯片工厂。

环境审查委员会(一个跨政府和学术环境监管机构)于周三批准了该计划。熟悉该计划的消息人士告诉日经亚洲,这为台积电在 2022 年初开始建设该设施并在 2023 年开始安装生产设备扫清了道路。

“半导体是对台湾经济增长最重要的产业之一,”中国台湾经济部门官员林全能在环境审查委员会会议上说。“政府将帮助台积电实现其环保目标,同时继续打造先进技术。”

美国顶级芯片制造商英特尔(台积电的客户和竞争对手)周二表示,其目标是到 2024 年生产世界上最先进的芯片,并在次年从台积电和三星电子等亚洲竞争对手手中夺回全球芯片桂冠。

今年早些时候,在全球短缺的情况下,包括德国、日本和美国在内的汽车制造经济体都向台湾施压,要求台湾增加汽车芯片的产量,这凸显了台湾作为先进半导体来源的重要性。

台湾政府将其芯片生产专长视为一种战略优势,可以保护该岛免受任何地缘政治冲突的影响。

政府官员告诉日经亚洲,台积电将部分生产从台湾推向全球多元化发展的举动将削弱台湾的长期战略重要性,这使得台湾将公司最尖端的生产技术保留在岛内变得更加重要。

一位熟悉台湾政府想法的政府消息人士告诉日经:“台积电扩大海外版图是可以的,但从地缘政治的角度来看,让台积电在台湾建立最先进的技术对台湾来说非常重要。所以台湾不会阻碍台积电保持竞争优势的计划。”

计划中的2纳米芯片厂将位于新竹宝山镇,占地近50亩。预计每天将使用 98,000 吨水,约占台积电 2020 年每日总用水量的 50%。“半导体是对台湾经济增长最重要的产业之一,”经济部副部长林传能在环境审查委员会会议上说。“政府将帮助台积电实现其环保目标,同时继续打造先进技术。”

美国顶级芯片制造商英特尔(台积电的客户和竞争对手)周二表示,其目标是到 2024 年生产世界上最先进的芯片,并在次年从台积电和三星电子等亚洲竞争对手手中夺回全球芯片桂冠。

今年早些时候,在全球短缺的情况下,包括德国、日本和美国在内的汽车制造经济体都向台湾施压,要求台湾增加汽车芯片的产量,这凸显了台湾作为先进半导体来源的重要性。

台湾政府将其芯片生产专长视为一种战略优势,可以保护该岛免受任何地缘政治冲突的影响。

政府官员告诉日经亚洲,台积电将部分生产从台湾多元化的举动将削弱台湾的长期战略重要性,这使得台湾将公司最尖端的生产技术保留在陆上变得更加重要。

一位熟悉蔡英文政府想法的政府消息人士告诉日经:“台积电扩大海外版图是可以的,但从地缘政治的角度来看,让台积电在[国内]建立最先进的技术对台湾来说非常重要。”亚洲。“我们不能阻碍台积电保持竞争优势的计划。”

计划中的2纳米芯片厂将位于新竹宝山镇,占地近50亩。预计每天将使用 98,000 吨水,约占台积电 2020 年每日总用水量的 50%。预计将创造2,500个工作机会。

宝山2期扩建历经4次专案小组审查,新竹居民及环团对于半导体产业高耗能、高耗水特性,及后续的废弃物处理多所疑虑。因竹科管理局承诺2030要达到100%使用再生水,28日进一步提出分阶段目标,2025年使用10%、2026年使用25%、2027年使用50%、2028年使用75%,直到2030年达100%目标。

再生能源方面,竹科也承诺,2050年将使用100%再生能源,营运后每年取得实际用电量25%再生能源。

这家芯片制造商承诺到 2025 年使用 10% 的再生水,到 2030 年在宝山新工厂使用 100% 的再生水.

台积电去年未能实现其在用水和废物产生方面的内部可持续发展目标,因为这家全球最大的半导体公司提高了该行业最先进芯片的产量。

台积电正在亚利桑那州建设 5 纳米芯片工厂,扩大其在中国南京的 28 纳米产能,并正在关注日本和德国的新工厂。

这家芯片制造商告诉日经亚洲,很高兴该项目获得了监管部门的批准,并将继续致力于绿色制造。

在 2021 年 6 月的 VLSI 技术和电路研讨会上,举办了一个关于“面向 2nm-CMOS 和新兴存储器的先进工艺和器件技术”的短期课程。在本文中,我将回顾前两个介绍前沿逻辑器件的演讲。这两个演示文稿是互补的,并提供了对逻辑技术可能发展的出色概述。

平面 MOSFET 的栅极长度 (Gate length:Lg) 缩放限制在大约 25nm,因为单表面栅极(single surface gate)对亚表面泄漏( sub surface leakage)的控制很差。

添加更多的栅极(例如在 FinFET 中),将使其中的沟道被限制在三个栅极之间,从而能够将 Lg 缩放到沟道厚度的大约 2.5 倍。FinFET 已经从英特尔最初采用的高度倾斜鳍壁(highly sloped fin walls )的 22 纳米发展到今天更加垂直的壁(vertical walls)和台积电为其 5 纳米工艺实施的高迁移率沟道 FinFET。

更高的鳍会增加有效沟道宽度 (effective channel width:Weff),Weff = 2Fh + Fth,其中 Fh 是鳍(Fin)高度,Fth 是鳍(Fin)厚度。增加 Weff 会增加重载电路(heavily loaded circuits)的驱动电流,但过高的鳍会浪费有源功率(active power)。直而薄的鳍片有利于短沟道效应(short channel effects),但 Fw 受到迁移率降低和阈值电压可变性(threshold voltage variability)增加的限制。在他们的 5nm 技术中实施高迁移率沟道(作者指出,用于 pFET 鳍片的 SiGe)使 TSMC 的驱动电流提高了约 18%。

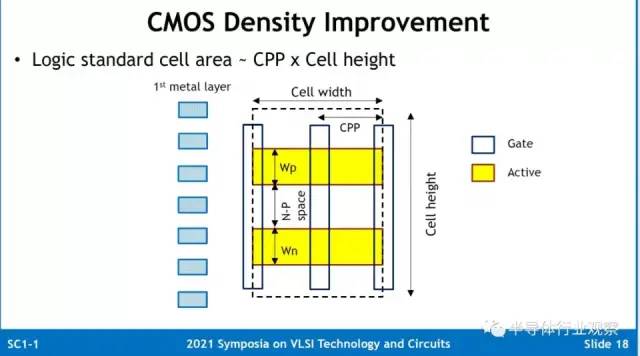

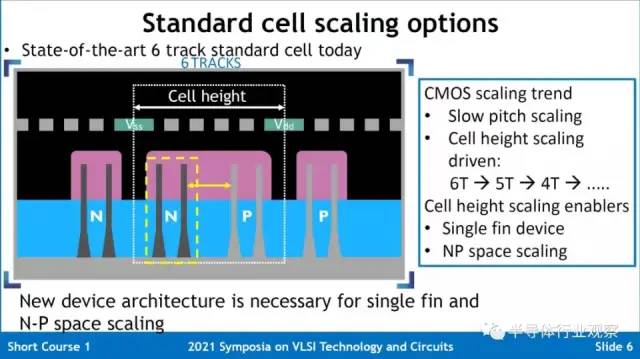

随着器件按比例缩小,寄生电阻和电容又将成为一个新问题。CPP(Contacted Poly Pitch)决定标准cell宽度(见图 1),它是由 Lg、接触宽度 (Contact Width :Wc) 和垫片厚度 ( Spacer Thickness:Tsp) 组成,CPP = Lg + Wc + 2Tsp。减少 Wc 会增加寄生电阻,除非进行工艺改进以改善接触,而减少 tsp 会增加寄生电容,除非使用较慢的介电常数间隔物。

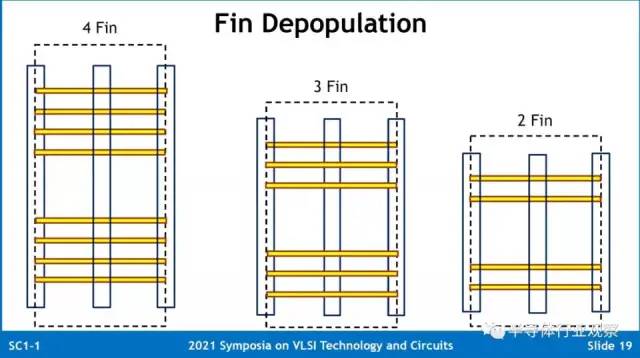

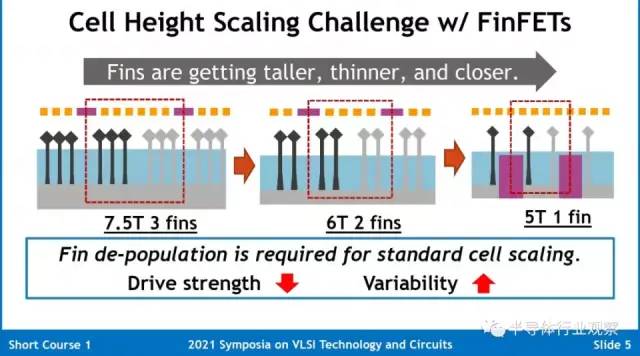

随着标准cell高度的降低,每个器件的鳍片数量必须减少(鳍片减少),见图 2。

Fin depopulation 减少了单元尺寸,增加了逻辑密度并提供了更高的速度和更低的功率,但它确实降低了驱动电流。

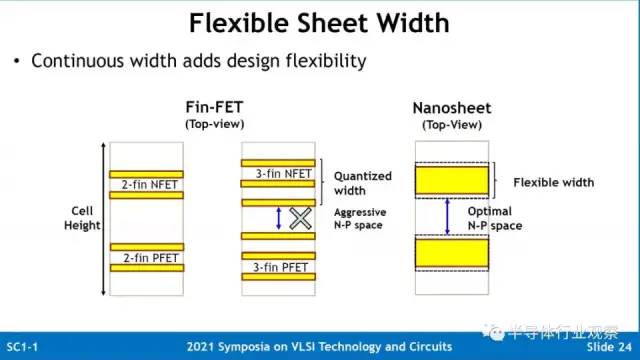

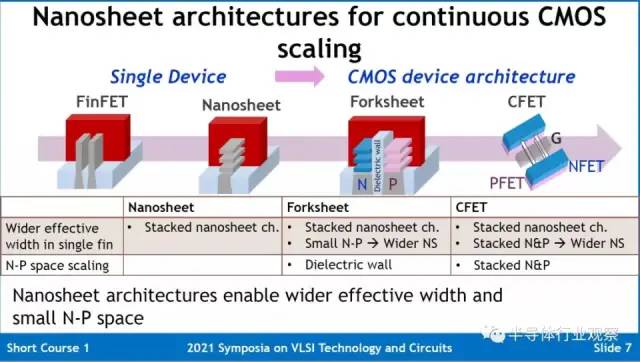

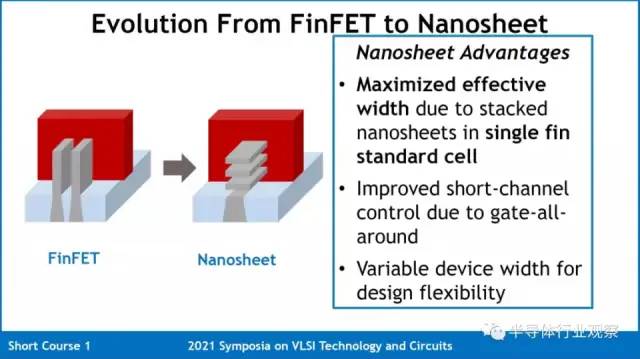

从 FinFET 过渡到堆叠的水平纳米片 (stacked Horizontal Nanosheets:HNS),通过改变片宽(sheet width:见图 3)和通过堆叠更多片来增加 Weff 的能力来提高灵活性。

添加sheets与 Weff 相加,Wee = N*2(W+H),其中 N 为sheets的数量,W 为sheets的宽度,H 为sheets的高度(厚度)。最终,sheets的数量受到底部sheets性能的限制。sheets之间的间距随着寄生电阻和电容的减小而降低,但必须足够大以使栅极金属(gate metals)和电介质(dielectric)进入间隙(gap)。在 HNS 堆栈下方有一个底部寄生台面器件( bottom parasitic mesa device),可以通过注入或介电层进行控制。

在 FinFET 中,nFET 电子迁移率高于 pFET 空穴迁移率。在 HNS 中,迁移率更加不平衡,电子迁移率更高,空穴迁移率更低。可以通过用 SiGe 包覆沟道(cladding the channel )或使用应变松弛缓冲器( Strain Relaxed Buffer)来提高空穴迁移率,但这两种技术都会增加工艺复杂性。

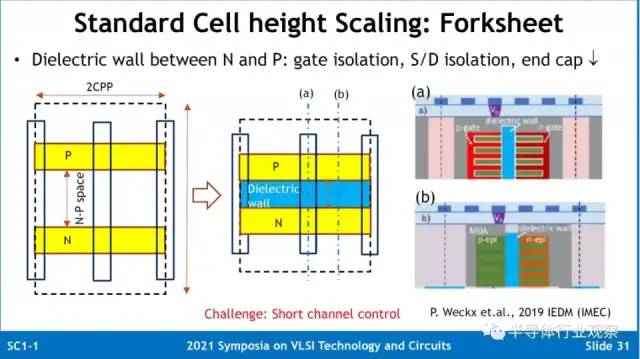

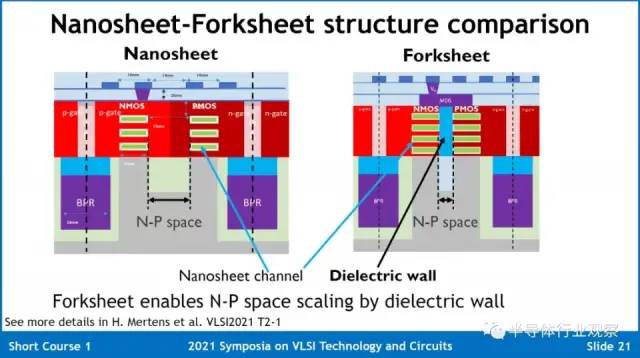

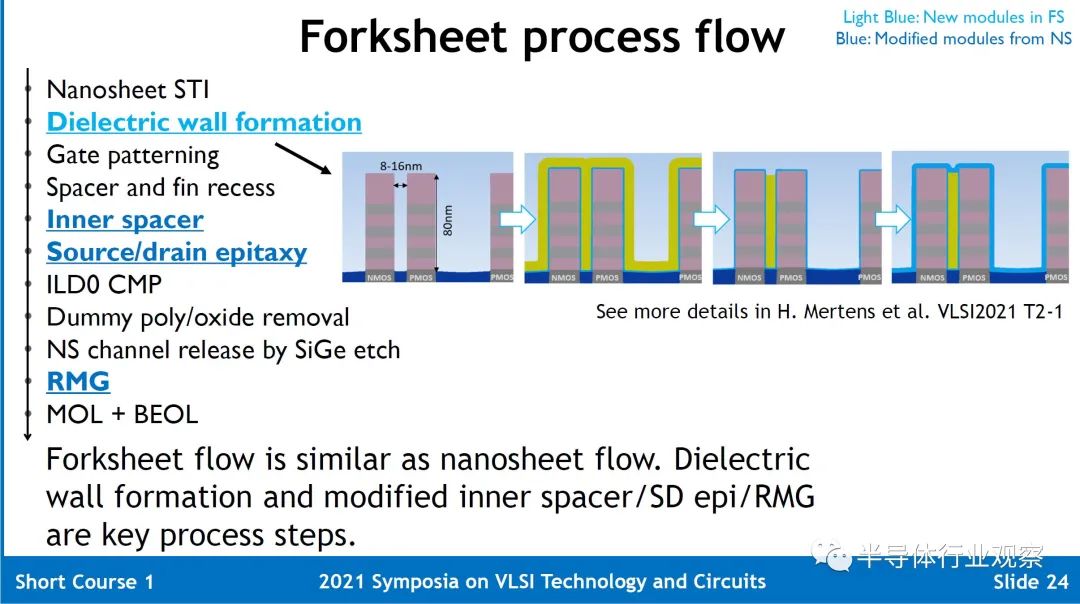

Imec 引入了一个称为 Forksheet (FS) 的概念,其中在 nFET 和 pFET 之间放置了一个介电层,从而减少了 np 间距,从而形成了更紧凑的标准单元,见图 4。

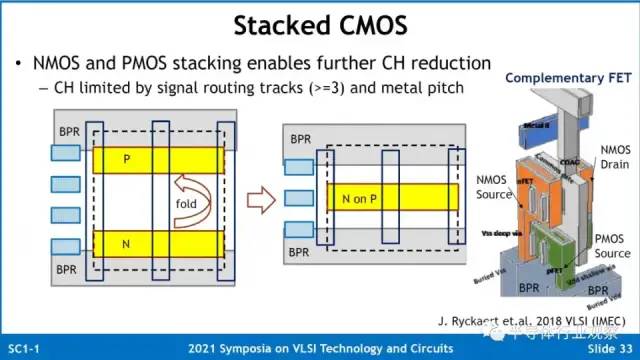

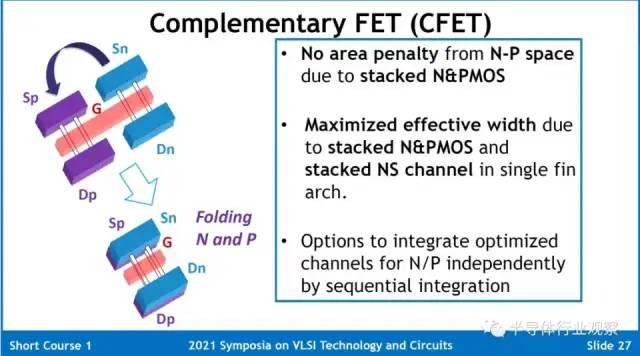

除了具有 FS 的 HNS,还有CFET(Complementary FET ),后者堆叠 nFET 和 pFET,从而无需水平 np 间距。

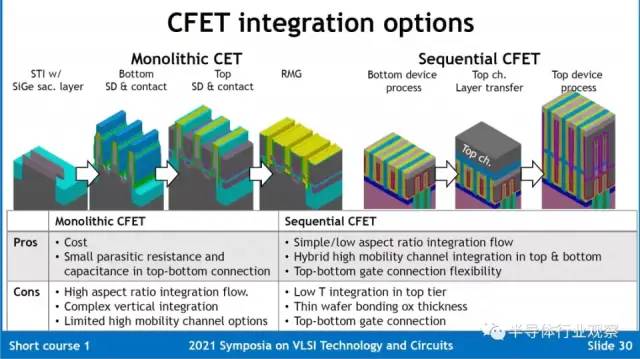

CFET 选项包括单片集成(monolithic integration),其中的 nFET 和 pFET 器件都制造在同一晶圆上。此外还有顺序集成(equential integration),其中的 nFET 和 pFET 制造在单独的晶圆上,然后结合在一起,这两种选择都有多个挑战仍在研究中。

除了 CFET,演讲者还谈到了将晶体管集成到后端 (Back End Of Line:BEOL) 互连中的 3D 集成。这些选项需要具有多晶硅沟道(polysilicon channels )或氧化物半导体的低温晶体管,这会带来各种性能和集成挑战。

在前端 (Front End Of Line:FEOL) 中,正在探索 CFET 之外的选项,例如高迁移率材料、隧道 FET (Tunnel FETs:TFET)、负电容 FET (Negative Capacitance FETs:NCFET)、低温 CMOS (Cryogenic CMOS)和低维材料(dimensional materials)。

低维材料采用纳米管或二维材料的形式,这些材料提供比 HNS 更短的 Lg 和更低的功率,但仍处于早期研究阶段。低维材料也适用于 HNS/CFET 方法,可选择堆叠许多层。

随着 FinFET 达到极限,鳍变得越来越高、越来越薄、越来越近。鳍片数量减少正在降低驱动电流并增加可变性,见图 6。

当今最先进的技术是每个设备有 2 个鳍片的 6 轨单元(track cell)。转向单鳍和更窄的 np 间距将需要新的器件架构来提高性能,见图 7。

为了继续 CMOS 缩放,我们需要从 FinFET sot HNS 过渡到具有 FS 和 CFET 的 HNS,见图 8。

从 FinFET 过渡到 HNS 提供了几个优势,大的 Weff,改进的短沟道效应,这意味着更短的 Lg 和更好的设计灵活性,因为能够改变片宽,见图 9。

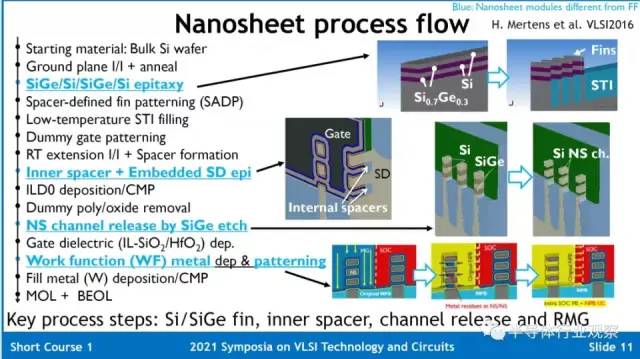

演讲者继续详细介绍 HNS 处理以及一些挑战和可能的解决方案。除了四个主要模块外,HNS 工艺与 FinFET 工艺非常相似,见图 10。

尽管 HNS 流程类似于 FinFET 流程,但不同的关键模块很困难。释放蚀刻和实现多个阈值电压特别困难。关于 HNS 所需的流程模块更改的细节,有很多很好的信息,这超出了像这样的评论文章的范围。没有明确讨论的一件事是,为了将 HNS 工艺扩展到 5 轨单元,需要埋入式电源轨 (Buried Power Rails:BPR),这是另一个仍在开发中的困难工艺模块。

正如在之前的演示中所见,FS 可以实现 HNS 的进一步扩展。图 11 展示了介电壁如何微缩( dielectric wall) HNS 单元的更详细视图。

图 11. 水平 Nanosheet/Forksheet 架构比较。

FS 工艺需要插入介电壁以减小 np 间距,图 12 说明了工艺流程。

除了 FS,CFET 通过堆叠器件提供零水平 np 间距。图 13. 说明了 CFET 概念。

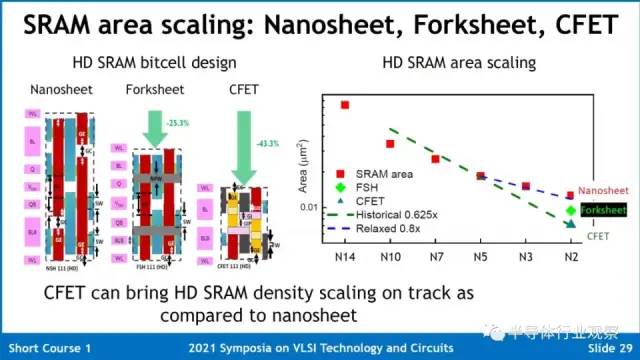

CFET 对于 SRAM 缩放特别有趣。SRAM 缩放已经放缓并且跟不上逻辑缩放。CFET 提供了将 SRAM 缩放恢复到历史趋势的潜力,见图 14。

图 14. 使用 CFET 进行 SRAM 缩放。

如前所述,有两种 CFET 制造方法,单片和顺序。图 15 对比了这两种方法的优缺点。

★ 点击文末【阅读原文】,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2750内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

个人中心

个人中心

我是园区

我是园区